| FindBook |

有 1 項符合

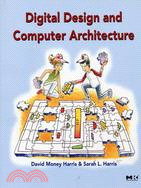

DIGITAL DESIGN AND COMPUTER ARCHITECTURE的圖書 |

|

DIGITAL DESIGN AND COMPUTER ARCHITECTURE 作者:DAVID MONEY HARRIS 出版社:全華圖書股份有限公司(全華經銷) 出版日期:2007-03-02 規格:23*20.5cm / 569頁 |

| 圖書館借閱 |

| 國家圖書館 | 全國圖書書目資訊網 | 國立公共資訊圖書館 | 電子書服務平台 | MetaCat 跨館整合查詢 |

| 臺北市立圖書館 | 新北市立圖書館 | 基隆市公共圖書館 | 桃園市立圖書館 | 新竹縣公共圖書館 |

| 苗栗縣立圖書館 | 臺中市立圖書館 | 彰化縣公共圖書館 | 南投縣文化局 | 雲林縣公共圖書館 |

| 嘉義縣圖書館 | 臺南市立圖書館 | 高雄市立圖書館 | 屏東縣公共圖書館 | 宜蘭縣公共圖書館 |

| 花蓮縣文化局 | 臺東縣文化處 |

|

|

- 圖書簡介

Digital Design and Computer Architecture is designed for courses that combine digital logic design with computer organization/architecture or that teach these subjects as a two-course sequence. Digital Design and Computer Architecture begins with a modern approach by rigorously covering the fundamentals of digital logic design and then introducing Hardware Description Languages (HDLs). Featuring examples of the two most widely-used HDLs, VHDL and Verilog, the first half of the text prepares the reader for what follows in the second: the design of a MIPS Processor. By the end of Digital Design and Computer Architecture, readers will be able to build their own microprocessor and will have a top-to-bottom understanding of how it works--even if they have no formal background in design or architecture beyond an introductory class. David Harris and Sarah Harris combine an engaging and humorous writing style with an updated and hands-on approach to digital design.

- 目次

1 From Zero to One

1.1 The Game Plan

1.2 The Art of Managing Complexity

1.3 The Digital Abstraction

1.4 Number Systems

1.5 Logic Gates

1.6 Logic Levels

1.7 CMOS Transistors

1.8 Power Consumption

1.9 Summary and A Look Ahead2 Combinational Logic Design

2.1 Introduction

2.2 Boolean Equations

2.3 Boolean Algebra

2.4 From Logic to Gates

2.5 Multilevel Combinational Logic

2.6 X's and Z's, Oh My

2.7 Karnaugh Maps

2.8 Combinational Building Blocks

2.9 Timing

2.10 Summary3 Sequential Logic Design

3.1 Introduction

3.2 Latches and Flip-Flops

3.3 Synchronous Logic Design

3.4 Finite State Machines

3.5 Timing of Sequential Logic

3.6 Parallelism

3.7 Summary4 Hardware Description Languages

4.1 Introduction

4.2 Combinational Logic

4.3 Structural Modeling

4.4 Sequential Logic

4.5 More Combinational Logic

4.6 Finite State Machines

4.7

Parameterized Modules

4.8 Testbenches

4.9 Summary5 Digital Building Blocks

5.1 Introduction

5.2 Arithmetic Circuits

5.3 Number Systems

5.4 Sequential Building Blocks

5.5 Memory Arrays

5.6 Logic Arrays

5.7 Summary6 Architecture

6.1 Introduction

6.2 Assembly Language

6.3 Machine Language

6.4 Programming

6.5 Addressing Modes

6.6 Lights, Camera, Action: Compiling, Assembling, and Loading

6.7 Odds and Ends

6.8 Real World Perspective: IA-32 Architecture

6.9 Summary7 Microarchitecture

7.1 Introduction

7.2 Performance Analysis

7.3 Single-Cycle Processor

7.4 Multicycle Processor

7.5 Pipelined Processor

7.6 HDL Representation

7.7 Exceptions

7.8 Advanced Microarchitecture

7.9 Real World Perspective: IA-32 Microarchitecture

7.10 Summary8 Memory Systems

8.1 Introduction

8.2 Memory System Performance Analysis

8.3 Caches

8.4 Virtual Memory

8.5 Memory-Mapped I/O

8.6 Real World Perspective: IA-32 Memory and I/O Systems

8.7 SummaryAppendix A Digital System Implementation

A.1 Introduction

A.2 74xx Logic

A.3 Programmable Logic

A.4 Application-Specific Integrated Circuits

A.5 Data Sheets

A.6 Logic Families

A.7 Packaging and Assembly

A.8 Transmission lines

A.9 EconomicsAppendix B MIPS Instructions

|