| FindBook |

有 5 項符合

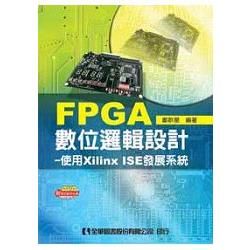

FPGA數位邏輯設計:使用Xilinx ISE發展系統(附程式範例光碟)的圖書 |

|

FPGA數位邏輯設計:使用Xilinx ISE發展系統 作者:鄭群星 出版社:全華圖書 出版日期:2010-01-06 語言:繁體中文 規格:平裝 / 704頁 / 16K / 普級 / 單色印刷 / 初版 |

| 圖書選購 |

| 型式 | 價格 | 供應商 | 所屬目錄 | $ 522 |

應用科學 |

$ 551 |

中文書 |

$ 551 |

科學科普 |

$ 551 |

高等教育 |

$ 580 |

資訊學群 |

|---|

| 圖書館借閱 |

| 國家圖書館 | 全國圖書書目資訊網 | 國立公共資訊圖書館 | 電子書服務平台 | MetaCat 跨館整合查詢 |

| 臺北市立圖書館 | 新北市立圖書館 | 基隆市公共圖書館 | 桃園市立圖書館 | 新竹縣公共圖書館 |

| 苗栗縣立圖書館 | 臺中市立圖書館 | 彰化縣公共圖書館 | 南投縣文化局 | 雲林縣公共圖書館 |

| 嘉義縣圖書館 | 臺南市立圖書館 | 高雄市立圖書館 | 屏東縣公共圖書館 | 宜蘭縣公共圖書館 |

| 花蓮縣文化局 | 臺東縣文化處 |

|

|

內容簡介

目錄

第1章 使用FPGA晶片設計數位邏輯 系統的方法

1-1 什麼是FPGA

1-2 FPGA晶片的發展過程及其基本架構

1-2-1 PLD之基本架構

1-2-2 PLD的種類

1-3 Xilinx FPGA的基本架構

1-3-1 Xilinx Spartan-3AN FPGA的基本架構

1-4 Xilinx Spartan-3AN FPGA晶片編號代表的意義

1-5 傳統設計數位邏輯系統的方法

1-6 使用FPGA設計數位邏輯系統的方法

1-6-1 使用繪圖方式設計數位邏輯系統的方法

1-6-2 使用VHDL硬體描述語言設計數位邏輯系統之方法

1-6-3 使用Verilog硬體描述語言設計數位邏輯系統的方法

1-6-4 使用狀態機方式設計數位系統的方法

1-6-5 Xilinx ISE發展系統功能簡介

1-7 使用Xilinx ISE發展系統設計FPGA及CPLD操作方式的差異

1-8 Xilinx ISE Simulator簡介

1-9 ModelSim模擬器之簡介

第2章 Xilinx ISE WebPACK及ModelSim XE模擬器的下載及安裝

2-1 ISE WebPACK軟體之下載

2-2 ISE WebPACK軟體之安裝

2-3 Xilinx ISE WebPACK更新檔Service Pack之下載及安裝

2-4 ModelSim XE模擬器之下載及安裝

2-4-1 ModelSim XE模擬器之下載

2-4-2 ModelSim XE模擬器之安裝

2-4-3 ModelSim License檔的下載及安裝

第3章 Xilinx ISE之簡易操作 步驟介紹

3-1 如何進入Project Navigator視窗

3-2 Project Navigator視窗之功能介紹

3-3 如何建立新的專案

3-4 如何離開所建立的專案

3-5 如何開啟一個舊的專案

3-6 基本邏輯閘介紹

3-6-1 反閘之電路符號、布林代數表示式及其真值表

3-6-2 或閘之電路符號、布林代數表示式及其真值表

3-6-3 及閘之電路符號、布林代數表示式及其真值表

3-6-4 互斥或閘之電路符號、布林代數表示式及其真值表

3-7 基本邏輯閘設計

3-7-1 取出邏輯閘元件

3-7-2 緩衝器元件的取出

3-7-3 執行連線的動作

3-7-4 加入輸入輸出端點

3-7-5 在輸入輸出端點取名稱

3-8 基本邏輯閘功能模擬的執行

3-8-1 使用ISE Simulator的模擬方法

3-8-2 使用Modelsim模擬器模擬的方法

3-9 晶片實作

3-9-1 Implementation Constraints File的設定

3-9-2 Implement Design的執行

3-10 使用FPGA Editor檢視佈置與繞線

3-11 FPGA晶片資源利用報告的檢視

3-12 時序報告的檢視

3-13 時序模擬的執行

3-14 Configuration的執行

3-14-1 直接下載至FPGA晶片上

3-14-2 下載至FPGA晶片內部的Flash

3-14-3 直接下載至FPGA與下載至Flash的差異

3-15 以HDL硬體描述語言設計數位電路的方法

第4章 組合邏輯設計實習

4-1 編碼器之實驗

4-1-1 十進位對二進位編碼器實驗

4-1-2 繪圖方式的設計

4-1-3 Behavioral Simulation的執行

4-1-4 ModelSim模擬器之簡易操作

4-1-5 將十進位對二進位編碼器設計成一元件模組使用

4-1-6 十進位對二進位編碼器元件模組之模擬及下載

4-2 如何將建立的元件模組在別的專案中使用

4-3 解碼器實驗

4-3-1 BCD解碼器

4-3-2 使用繪圖方式的設計方法

4-3-3 ModelSim模擬器之進階操作

4-3-4 將BCD解碼器組成一元件模組使用

4-3-5 再使用ModelSim模擬電路之功能

4-3-6 二對四解碼器

4-4 解多工器之實驗

4-4-1 一對四解多工器之基本電路

4-5 多工器

4-5-1 四對一多工器

4-6 七段顯示器解碼器電路之設計

4-6-1 七段顯示器之基本架構

4-6-2 真值表

4-6-3 布林代數表示式

4-6-4 邏輯電路圖

4-6-5 使用Xilinx ECS繪圖

4-6-6 使用Modelsim執行電路功能模擬

4-6-7 匯流排信號之操作

4-6-8 將七段顯示器解碼電路設計成一元件模組使用

4-6-9 再使用Modelsim模擬SEG7CKT.sch電路之功能

4-6-10 Implementation Constraints File的執行

4-6-11 Implement Design的執行

4-6-12 時序模擬的執行

4-6-13 Configuration的執行

第5章 階層式電路的設計

5-1 壹位元半加器之設計

5-2 壹位元全加器之設計

5-2-1 壹位元全加器階層式電路之設計

5-3 二位元全加器之設計

第6章 循序邏輯電路設計

6-1 四位元非同步上數計數器之設計

6-2 不同頻率時鐘脈波產生電路之設計

6-3 具有七段顯示器解碼電路之四位元非同步上數計數器之設計

第7章 VHDL硬體描述語言設計方法

7-1 如何使用VHDL硬體描述語言的方式設計電路

7-1-1 使用ISE Text Editor編輯VHDL硬體描述語言設計電路的方法

7-1-2 使用ISE語言樣板設計VHDL硬體描述語言的方法

7-2 VHDL硬體描述語言的基本架構組成

7-2-1 Library宣告的格式

7-2-2 Use宣告的格式

7-2-3 Entity電路單體描述的格式

7-2-4 Architecture架構描述的格式

7-2-5 Structure宣告所使用之格式及範例

7-2-6 Dataflow描述之格式及範例

7-2-7 Behavioral行為描述之格式及範例

7-2-8 組成宣告描述之格式及範例

第8章 VHDL硬體描述語言之描述規則

8-1 VHDL硬體描述語言指令的命名規則

8-1-1 VHDL的註解描述

8-2 VHDL敘述的描述形式

8-3 VHDL的常用描述指令

8-3-1 F條件式

8-3-2 WHEN...ELSE敘述

8-3-3 Case...Is...When...when Others敘述

8-3-4 with...select...when...when others敘述

8-3-5 Loop敘述

8-3-6 NEXT敘述

8-3-7 Wait敘述

8-4 VHDL中所使用的運算子

8-5 VHDL的保留字

第9章 VHDL設計實例介紹

9-1 三對八解碼器的設計

9-2 十六進位上下數計數器之設計

9-2-1 除頻電路之設計

9-2-2 十六進位上下數計數器之設計

9-2-3 多工器之設計

9-2-4 七段顯示器解碼電路之設計

9-2-5 十六進位上下數計數器之完整電路設計

9-3 9999BCD上下計數器之設計

9-3-1 BCD上下計數器之設計

9-3-2 除頻電路、多工器、七段顯示器解碼電路模組之引入

9-3-3 BCD上下數計數電路之完整設計

9-4 跑馬燈之設計

第10章 Verilog硬體描述語言設計方法

10-1 Verilog硬體描述語言的基本架構

10-2 Verilog模組描述的基本格式

10-2-1 開關層次描述的實例介紹

10-2-2 邏輯間層次描述的實例介紹

10-2-3 資料流層次描述的實例介紹

10-2-4 行為層次描述的實例介紹

10-3 Verilog硬體描述語言的描述格式

10-3-1 Verilog的基本語法規定

10-3-2 Verilog的數字格式

10-3-3 Verilog的運算子

10-4 Verilog的資料型態

10-4-1 數值集(Value Set)

10-4-2 接線(net)

10-4-3 暫存器(reg)

10-4-4 向量(vectors)

10-4-5 整數(integer)

10-4-6 實數(real)

10-4-7 時間(time)

10-4-8 陣列(arrays)

10-4-9 記憶體(memories)

10-4-10 參數(parameters)

10-4-11 字串(strings)

10-4-12 三態(Tri-state)

10-5 Verilog的事件基礎時間控制

10-5-1 正規事件控制

10-5-2 事件或控制

10-6 Verilog的輸入輸出埠描述

10-7 Verilog的系統關鍵字描述

10-8 Verilog系統的暫停及完成模擬敘述

10-9 Verilog的監視顯示描述

10-10 Verilog的系統保留字

附錄一 MB-EVL-XC3S50AN-V11 FPGA開發板之介紹

A-1 Xilinx Spartan 3AN XC3S50AN-TQG144 FPGA晶片

A-2 輸入裝置

A-3 輸出裝置

A-4 J1及J2 使用者擴充I/O接腳插座

A-5 JTAG下載接頭JP3

A-6 JP1 Jumper下載模式跳線

A-7 S10 PROGB Push-Button Switch

A-8 電源開關S11

A-9 D1綠色LED

A-10 D13 紅色LED

A-11 J4電源整流器5V輸入接頭

A-12 直流電源指示LED D15 D16 D17

A-13 25pin Printer Port

附錄二 MB-EVL-XC2S50E-V10 FPGA開發板之介紹

附錄三 問題集

|