| FindBook |

有 3 項符合

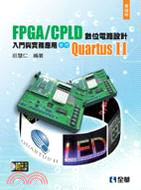

FPGA/CPLD 數位電路設計入門與實務應用:使用QuartusⅡ(附系統.範例光碟)(第四版)的圖書 |

|

FPGA/CPLD數位電路設計入門與實務應用:使用QUARTUS II 作者:莊慧仁 出版社:全華圖書 出版日期:2010-08-19 語言:繁體中文 規格:平裝 / 440頁 / 19.0*26.0 cm / 普級 / 單色印刷 / 初版 |

| 圖書選購 |

| 型式 | 價格 | 供應商 | 所屬目錄 | $ 378 |

應用科學 |

$ 399 |

專技人員考試 |

$ 399 |

高等教育 |

|---|

| 圖書館借閱 |

| 國家圖書館 | 全國圖書書目資訊網 | 國立公共資訊圖書館 | 電子書服務平台 | MetaCat 跨館整合查詢 |

| 臺北市立圖書館 | 新北市立圖書館 | 基隆市公共圖書館 | 桃園市立圖書館 | 新竹縣公共圖書館 |

| 苗栗縣立圖書館 | 臺中市立圖書館 | 彰化縣公共圖書館 | 南投縣文化局 | 雲林縣公共圖書館 |

| 嘉義縣圖書館 | 臺南市立圖書館 | 高雄市立圖書館 | 屏東縣公共圖書館 | 宜蘭縣公共圖書館 |

| 花蓮縣文化局 | 臺東縣文化處 |

|

|

圖書介紹 - 資料來源:TAAZE 讀冊生活 評分:

圖書名稱:FPGA/CPLD 數位電路設計入門與實務應用:使用QuartusⅡ(附系統.範例光碟)(第四版)

本書是一本簡單、易懂的數位電路設計及應用。書中軟體是以QuartusII5.1版做為開發平台並運用到數位電路設計。將理論數位電路與現今的FPGA/CPLD,透過電腦輔助設計工具相結合,使讀者可以應用各種編輯技術設計晶片外,更讓讀者了解如何將FPGA/CPLD應用在電子遊戲領域之晶片上。本書共有七章:包括QuartusII軟體安裝及設計簡介、算術邏輯電路設計、組合邏輯電路設計、計數器及除頻器設計、綜合練習設計、綜合應用專題以及具有Audio音效乒乓球遊戲實作等介紹。適用於大學、科大電子、電機、資工系「數位電

目錄

第1章 QuartusII軟體安裝及設計流程簡介1.1 QuartusII軟體安裝 1-11.2 QuartusII軟體介紹 1-111.3 QuartusII軟體基本功能介紹 1-131.3.1 電路圖編輯(SchematicEditor) 1-131.3.2 文字編輯(TextEditor) 1-141.3.3 專案編譯(Compiler) 1-151.3.4 波形編輯(WaveformEditor) 1-151.3.5 波形模擬(WaveformSimulator) 1-161.3.6 接腳編輯(P

»看全部

商品資料

- 作者: 莊慧仁

- 出版社: 全華圖書股份有限公司 出版日期:2010-08-19 ISBN/ISSN:9572175424

- 語言:繁體中文 裝訂方式:平裝 頁數:440頁

- 類別: 中文書> 政府考用> 專技人員考試

|