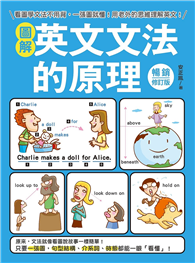

《半導體先進封裝技術》作者在半導體封裝領域擁有40多年的研發和製造經驗。《半導體先進封裝技術》共分為11章,重點介紹了先進封裝,系統級封裝,扇入型晶圓級/板級晶片尺寸封裝,扇出型晶圓級/板級封裝,2D、2.1D和2.3DIC集成,2.5DIC集成,3DIC集成和3DIC封裝,混合鍵合,芯粒異質集成,低損耗介電材料和先進封裝未來趨勢等內容。

通過對這些內容的學習,能夠讓讀者快速學會解決先進封裝問題的方法。《半導體先進封裝技術》可作為高等院校微電子學與固體電子學、電子科學與技術、積體電路科學與工程等專業的高年級本科生和研究生的教材和參考書,也可供相關領域的工程技術人員參考。

| FindBook |

有 1 項符合

半導體先進封裝技術的圖書 |

|

半導體先進封裝技術 作者:(美)劉漢誠 / 譯者:蔡堅 出版社:機械工業出版社 出版日期:2022-08-01 語言:簡體中文 規格:平裝 / 413頁 / 19 x 26 x 2.06 cm / 普通級/ 1-1 |

| 圖書館借閱 |

| 國家圖書館 | 全國圖書書目資訊網 | 國立公共資訊圖書館 | 電子書服務平台 | MetaCat 跨館整合查詢 |

| 臺北市立圖書館 | 新北市立圖書館 | 基隆市公共圖書館 | 桃園市立圖書館 | 新竹縣公共圖書館 |

| 苗栗縣立圖書館 | 臺中市立圖書館 | 彰化縣公共圖書館 | 南投縣文化局 | 雲林縣公共圖書館 |

| 嘉義縣圖書館 | 臺南市立圖書館 | 高雄市立圖書館 | 屏東縣公共圖書館 | 宜蘭縣公共圖書館 |

| 花蓮縣文化局 | 臺東縣文化處 |

|

|

圖書介紹 - 資料來源:博客來 評分:

圖書名稱:半導體先進封裝技術

內容簡介

作者介紹

劉漢誠(John H.Lau)博士

美國電氣電子工程師學會(IEEE)會士、美國機械工程師學會(ASME)會士及國際微電子與封裝學會(IMAPS)會士。他曾在美國加利福尼亞州惠普實驗室/安捷倫公司擔任資深科學家超過25年。他獲得了伊利諾大學厄巴納-香檳分校理論和應用力學博士學位;在半導體封裝領域擁有40多年的研發和製造經驗,研究領域為晶片異構集成、SiP、TSV、扇出型/扇入型晶圓級/板級封裝、MEMS、mini/ micro LED、3D IC集成、SMT和焊接力學等;發表500多篇論文,發明30多項專利,舉辦 300多場講座,撰寫20多部教科書;獲得ASME、IEEE、SME等學會頒發的多項榮譽。

美國電氣電子工程師學會(IEEE)會士、美國機械工程師學會(ASME)會士及國際微電子與封裝學會(IMAPS)會士。他曾在美國加利福尼亞州惠普實驗室/安捷倫公司擔任資深科學家超過25年。他獲得了伊利諾大學厄巴納-香檳分校理論和應用力學博士學位;在半導體封裝領域擁有40多年的研發和製造經驗,研究領域為晶片異構集成、SiP、TSV、扇出型/扇入型晶圓級/板級封裝、MEMS、mini/ micro LED、3D IC集成、SMT和焊接力學等;發表500多篇論文,發明30多項專利,舉辦 300多場講座,撰寫20多部教科書;獲得ASME、IEEE、SME等學會頒發的多項榮譽。

目錄

前言

第1章 先進封裝1

1.1 引言1

1.2 半導體的應用1

1.3 系統技術的驅動力1

1.3.1 AI 1

1.3.2 5G 2

1.4 先進封裝概述3

1.4.1 先進封裝種類3

1.4.2 先進封裝層級3

1.5 2D扇出型(先上晶)IC集成5

1.6 2D倒裝晶片IC集成5

1.7 PoP、SiP和異質集成6

1.8 2D扇出型(後上晶)IC集成8

1.9 2.1D倒裝晶片IC集成8

1.10 含互連橋的2.1D倒裝晶片IC集成9

1.11 含互連橋的2.1D扇出型IC集成9

1.12 2.3D扇出型(先上晶)IC集成10

1.13 2.3D倒裝晶片IC集成10

1.14 2.3D扇出型(後上晶)IC集成11

1.15 2.5D(C4凸點)IC集成12

1.16 2.5D(C2凸點)IC集成12

1.17 微凸點3D IC集成13

1.18 微凸點芯粒3D IC集成14

1.19 無凸點3D IC集成14

1.20 無凸點芯粒3D IC集成15

1.21 總結和建議15

參考文獻16

第2章 系統級封裝22

2.1 引言22

2.2 片上系統22

2.3 SiP概述23

2.4 SiP的使用目的23

2.5 SiP的實際應用23

2.6 SiP舉例24

2.7 SMT25

2.7.1 PCB26

2.7.2 SMD28

2.7.3 焊膏29

2.7.4 範本印刷焊膏和自動光學檢測30

2.7.5 SMD的拾取和放置32

2.7.6 對PCB上的SMD的AOI33

2.7.7 SMT焊料回流33

2.7.8 缺陷的AOI和X射線檢測34

2.7.9 返修35

2.7.10 總結和建議36

2.8 倒裝晶片技術36

2.8.1 基於範本印刷的晶圓凸點成型技術37

2.8.2 C4晶圓凸點成型技術38

2.8.3 C2晶圓凸點成型技術40

2.8.4 倒裝晶片組裝——C4/C2凸點批量回流(CUF)40

2.8.5 底部填充提升可靠性42

2.8.6 倒裝晶片組裝——C4/C2凸點的小壓力熱壓鍵合(CUF)44

2.8.7 倒裝晶片組裝——C2凸點的大壓力熱壓鍵合(NCP)45

2.8.8 倒裝晶片組裝——C2凸點的大壓力熱壓鍵合(NCF)45

2.8.9 一種先進的倒裝晶片組裝——C2凸點液相接觸熱壓鍵合47

2.8.10 總結和建議53

參考文獻54

第3章 扇入型晶圓級/板級晶片尺寸封裝63

3.1 引言63

3.2 扇入型晶圓級晶片尺寸封裝(WLCSP)65

3.2.1 封裝結構65

3.2.2 WLCSP的關鍵工藝步驟67

3.2.3 WLCSP在PCB上的組裝68

3.2.4 WLCSP在PCB上組裝的熱模擬68

3.2.5 總結和建議74

3.3 扇入型板級晶片尺寸封裝(PLCSP)75

3.3.1 測試晶片75

3.3.2 測試封裝體76

3.3.3 PLCSP工藝流程77

3.3.4 PLCSP的PCB組裝83

3.3.5 PLCSP PCB組裝的跌落試驗84

3.3.6 PLCSP PCB組裝的熱迴圈試驗86

3.3.7 PLCSP PCB組裝的熱迴圈模擬92

3.3.8 總結和建議95

3.4 6面模塑晶圓級晶片尺寸封裝96

3.4.1 星科金朋的eWLCSP97

3.4.2 聯合科技的WLCSP97

3.4.3 矽品科技的mWLCSP97

3.4.4 華天科技的WLCSP99

3.4.5 矽品科技和聯發科的mWLCSP99

3.4.6 總結和建議102

3.5 6面模塑板級晶片尺寸封裝102

3.5.1 6面模塑PLCSP的結構102

3.5.2 晶圓正面切割和EMC模塑104

3.5.3 背面減薄和晶圓背面模塑104

3.5.4 等離子體刻蝕和劃片106

3.5.5 測試的PCB106

3.5.6 6面模塑PLCSP在PCB上的SMT組裝106

3.5.7 6面模塑PLCSP的熱迴圈試驗108

3.5.8 6面模塑PLCSP的PCB組裝熱迴圈模擬111

3.5.9 總結和建議115

參考文獻115

第4章 扇出型晶圓級/板級封裝124

4.1 引言124

4.2 扇出型(先上晶且面朝下)晶圓級封裝(FOWLP)125

4.2.1 測試晶片125

4.2.2 測試封裝體126

4.2.3 傳統的先上晶(面朝下)晶圓級工藝127

4.2.4 異質集成封裝的新工藝128

4.2.5 幹膜EMC層壓128

4.2.6 臨時鍵合另一塊玻璃支撐片128

4.2.7 再佈線層130

4.2.8 焊球植球131

4.2.9 最終解鍵合131

4.2.10 PCB組裝134

4.2.11 異質集成的可靠性(跌落試驗)135

4.2.12 總結和建議137

4.3 扇出型(先上晶且面朝下)板級封裝(FOPLP)137

4.3.1 測試封裝體的異質集成138

4.3.2 一種新的Uni-SIP工藝140

4.3.3 ECM面板的幹膜層壓140

4.3.4 Uni-SIP結構的層壓141

4.3.5 新ABF的層壓、鐳射鑽孔、去膠渣141

4.3.6 鐳射直寫圖形和PCB鍍銅144

4.3.7 總結和建議145

4.4 扇出型(先上晶且面朝上)晶圓級封裝146

4.4.1 測試晶片146

4.4.2 工藝流程146

4.5 扇出型(先上晶且面朝上)板級封裝148

4.5.1 封裝結構148

4.5.2 工藝流程148

4.6 扇出型(後上晶或先RDL)晶圓級封裝150

4.6.1 IME的先RDL FOWLP151

4.6.2 測試結構151

4.6.3 先RDL關鍵工藝步驟152

4.6.4 先RDL FOWLP的PCB組裝154

4.7 扇出型(後上晶或先RDL)板級封裝154

4.7.1 測試晶片154

4.7.2 測試封裝體154

4.7.3 異質集成用先RDL板級封裝157

4.7.4 RDL基板的製作157

4.7.5 晶圓凸點成型160

4.7.6 晶片-基板鍵合160

4.7.7 底部填充和EMC模塑162

4.7.8 面板/條帶轉移163

4.7.9 阻焊層開窗和表面處理163

4.7.10 植球、解鍵合和條帶切割163

4.7.11 先RDL板級封裝的PCB組裝165

4.7.12 跌落試驗結果和失效分析165

4.7.13 熱迴圈試驗結果和失效分析169

4.7.14 熱迴圈模擬174

4.7.15 總結和建議175

4.8 Mini-LED RGB顯示器的扇出型板級封裝176

4.8.1 測試mini-LED177

4.8.2 測試mini-LED RGB顯示器的SMD封裝178

4.8.3 RDL和mini-LED RGB SMD製造179

4.8.4 PCB組裝182

4.8.5 跌落試驗185

4.8.6 熱迴圈模擬185

4.8.7 總結和建議191

參考文獻191

第5章 2D、2.1D和2.3D IC集成200

5.1 引言200

5.2 2D IC集成——引線鍵合200

5.3 2D IC集成——倒裝晶片201

5.4 2D IC集成——引線鍵合和倒裝晶片201

5.5 RDL202

5.5.1 有機RDL202

5.5.2 無機RDL202

5.5.3 混合RDL202

5.6 2D IC集成——扇出型(先上晶)203

5.6.1 HTC的Desire 606W203

5.6.2 4顆晶片異質集成203

5.7 2D IC集成——扇出型(後上晶)205

5.7.1 IME的後上晶扇出型封裝205

5.7.2 Amkor的SWIFT206

5.7.3 Amkor的SLIM207

5.7.4 矽品科技的混合RDL扇出208

5.7.5 欣興電子的扇出型後上晶工藝209

5.8 2.1D IC集成210

5.8.1 Shinko的i-THOP210

5.8.2 日立的2.1D有機轉接板212

5.8.3 日月光的2.1D有機轉接板212

5.8.4 矽品科技的2.1D有機轉接板213

5.8.5 長電科技的uFOS215

5.8.6 英特爾的EMIB216

5.8.7 應用材料的互連橋217

5.8.8 台積電的LSI217

5.9 2.3D IC集成217

5.10 採用SAP/PCB法的2.3D IC集成218

5.10.1 Shinko的無芯板有機轉接板218

5.10.2 思科的有機轉接板219

5.11 採用扇出型(先上晶)技術的2.3D IC集成220

5.11.1 星科金朋的2.3D eWLB220

5.11.2 聯發科的扇出型(先上晶)技術222

5.11.3 日月光的FOCoS(先上晶)223

5.11.4 台積電的InFO_oS和InFO_MS224

5.12 採用扇出型(後上晶)技術的2.3D IC集成225

5.12.1 矽品科技的NTI225

5.12.2 三星的無矽RDL轉接板225

5.12.3 日月光的FOCoS(後上晶)228

5.12.4 台積電的多層RDL轉接板229

5.12.5 Shinko的2.3D有機轉接板229

5.12.6 欣興電子的2.3D RDL轉接板232

5.13 總結和建議247

參考文獻247

第6章 2.5D IC集成251

6.1 引言251

6.2 Leti的SoW技術(2.5D IC集成技術的起源)251

6.3 IME的2.5D IC集成技術252

6.3.1 2.5D IC集成的三維非線性局部及全域分析252

6.3.2 用於電氣和流體互連的2.5D IC集成技術254

6.3.3 雙面堆疊無源TSV轉接板256

6.3.4 作為應力(可靠性)緩衝的TSV轉接板257

6.4 中國香港科技大學雙面集成晶片的TSV轉接板技術258

6.5 中國臺灣“工業技術研究院”的2.5D IC集成259

6.5.1 雙面集成晶片TSV轉接板的熱管理259

6.5.2 應用於LED含嵌入式流體微通道的TSV轉接板260

6.5.3 集成有片上系統和存儲立方的TSV轉接板262

6.5.4 半嵌入式TSV轉接板263

6.5.5 雙面粘接晶片的TSV轉接板264

6.5.6 雙面集成晶片的TSV轉接板266

6.5.7 TSH轉接板268

6.6 台積電的CoWoS技術270

6.7 賽靈思/台積電的2.5D IC集成270

6.8 Altera/台積電的2.5D IC集成273

6.9 AMD/聯電的2.5D IC集成273

6.10 英偉達/台積電的2.5D IC集成274

6.11 台積電CoWoS路線圖275

6.12 2.5D IC集成的近期進展276

6.12.1 台積電的集成有深槽電容CoWoS276

6.12.2 IME 2.5D IC集成的非破壞性失效定位方法277

6.12.3 Fraunhofer的光電轉接板277

6.12.4 Dai Nippon/AGC的玻璃轉接板278

6.12.5 富士通的多層玻璃轉接板280

6.13 總結和建議280

參考文獻281

第7章 3D IC集成和3D IC封裝287

7.1 引言287

7.2 3D IC封裝287

7.2.1 3D IC封裝——引線鍵合式存儲晶片堆疊287

7.2.2 3D IC封裝——面對面鍵合後引線鍵合到基板291

7.2.3 3D IC封裝——背對背鍵合後引線鍵合到基板292

7.2.4 3D IC封裝——面對面鍵合後通過凸點/焊球到基板上293

7.2.5 3D IC封裝——面對背296

7.2.6 3D IC封裝——SiP中的埋入式晶片(面對面)296

7.2.7 3D IC封裝——採用倒裝晶片技術的PoP298

7.2.8 3D IC封裝——採用扇出技術的PoP300

7.2.9 總結和建議303

7.3 3D IC集成303

7.3.1 3D IC集成——HBM標準303

7.3.2 3D IC集成——HBM組裝305

7.3.3 3D IC集成——採用TSV的晶片堆疊307

7.3.4 3D IC集成——採用TSV的無凸點混合鍵合晶片堆疊311

7.3.5 3D IC集成——無TSV的無凸點混合鍵合晶片堆疊313

7.3.6 總結和建議313

參考文獻314

第8章 混合鍵合319

8.1 引言319

8.2 Cu-Cu TCB319

8.2.1 Cu-Cu TCB的一些基本原理319

8.2.2 IBM/RPI的Cu-Cu TCB321

8.3 室溫Cu-Cu TCB321

8.3.1 室溫Cu-Cu TCB的一些基本原理321

8.3.2 NIMS/AIST/東芝/東京大學的室溫Cu-Cu TCB322

8.4 SiO2-SiO2 TCB322

8.4.1 SiO2-SiO2 TCB的一些基本原理322

8.4.2 麻省理工學院的SiO2-SiO2 TCB324

8.4.3 Leti/ 飛思卡爾/意法半導體的SiO2-SiO2 TCB325

8.5 低溫DBI326

8.5.1 低溫DBI的一些基本原理326

8.5.2 有TSV的索尼CMOS圖像感測器328

8.5.3 無TSV(混合鍵合)的索尼CMOS圖像感測器329

8.6 低溫混合鍵合的近期發展332

8.6.1 IME混合鍵合的熱機械性能332

8.6.2 台積電的混合鍵合335

8.6.3 IMEC的混合鍵合338

8.6.4 格羅方德的混合鍵合339

8.6.5 三菱的混合鍵合340

8.6.6 Leti的混合鍵合341

8.6.7 英特爾的混合鍵合343

第1章 先進封裝1

1.1 引言1

1.2 半導體的應用1

1.3 系統技術的驅動力1

1.3.1 AI 1

1.3.2 5G 2

1.4 先進封裝概述3

1.4.1 先進封裝種類3

1.4.2 先進封裝層級3

1.5 2D扇出型(先上晶)IC集成5

1.6 2D倒裝晶片IC集成5

1.7 PoP、SiP和異質集成6

1.8 2D扇出型(後上晶)IC集成8

1.9 2.1D倒裝晶片IC集成8

1.10 含互連橋的2.1D倒裝晶片IC集成9

1.11 含互連橋的2.1D扇出型IC集成9

1.12 2.3D扇出型(先上晶)IC集成10

1.13 2.3D倒裝晶片IC集成10

1.14 2.3D扇出型(後上晶)IC集成11

1.15 2.5D(C4凸點)IC集成12

1.16 2.5D(C2凸點)IC集成12

1.17 微凸點3D IC集成13

1.18 微凸點芯粒3D IC集成14

1.19 無凸點3D IC集成14

1.20 無凸點芯粒3D IC集成15

1.21 總結和建議15

參考文獻16

第2章 系統級封裝22

2.1 引言22

2.2 片上系統22

2.3 SiP概述23

2.4 SiP的使用目的23

2.5 SiP的實際應用23

2.6 SiP舉例24

2.7 SMT25

2.7.1 PCB26

2.7.2 SMD28

2.7.3 焊膏29

2.7.4 範本印刷焊膏和自動光學檢測30

2.7.5 SMD的拾取和放置32

2.7.6 對PCB上的SMD的AOI33

2.7.7 SMT焊料回流33

2.7.8 缺陷的AOI和X射線檢測34

2.7.9 返修35

2.7.10 總結和建議36

2.8 倒裝晶片技術36

2.8.1 基於範本印刷的晶圓凸點成型技術37

2.8.2 C4晶圓凸點成型技術38

2.8.3 C2晶圓凸點成型技術40

2.8.4 倒裝晶片組裝——C4/C2凸點批量回流(CUF)40

2.8.5 底部填充提升可靠性42

2.8.6 倒裝晶片組裝——C4/C2凸點的小壓力熱壓鍵合(CUF)44

2.8.7 倒裝晶片組裝——C2凸點的大壓力熱壓鍵合(NCP)45

2.8.8 倒裝晶片組裝——C2凸點的大壓力熱壓鍵合(NCF)45

2.8.9 一種先進的倒裝晶片組裝——C2凸點液相接觸熱壓鍵合47

2.8.10 總結和建議53

參考文獻54

第3章 扇入型晶圓級/板級晶片尺寸封裝63

3.1 引言63

3.2 扇入型晶圓級晶片尺寸封裝(WLCSP)65

3.2.1 封裝結構65

3.2.2 WLCSP的關鍵工藝步驟67

3.2.3 WLCSP在PCB上的組裝68

3.2.4 WLCSP在PCB上組裝的熱模擬68

3.2.5 總結和建議74

3.3 扇入型板級晶片尺寸封裝(PLCSP)75

3.3.1 測試晶片75

3.3.2 測試封裝體76

3.3.3 PLCSP工藝流程77

3.3.4 PLCSP的PCB組裝83

3.3.5 PLCSP PCB組裝的跌落試驗84

3.3.6 PLCSP PCB組裝的熱迴圈試驗86

3.3.7 PLCSP PCB組裝的熱迴圈模擬92

3.3.8 總結和建議95

3.4 6面模塑晶圓級晶片尺寸封裝96

3.4.1 星科金朋的eWLCSP97

3.4.2 聯合科技的WLCSP97

3.4.3 矽品科技的mWLCSP97

3.4.4 華天科技的WLCSP99

3.4.5 矽品科技和聯發科的mWLCSP99

3.4.6 總結和建議102

3.5 6面模塑板級晶片尺寸封裝102

3.5.1 6面模塑PLCSP的結構102

3.5.2 晶圓正面切割和EMC模塑104

3.5.3 背面減薄和晶圓背面模塑104

3.5.4 等離子體刻蝕和劃片106

3.5.5 測試的PCB106

3.5.6 6面模塑PLCSP在PCB上的SMT組裝106

3.5.7 6面模塑PLCSP的熱迴圈試驗108

3.5.8 6面模塑PLCSP的PCB組裝熱迴圈模擬111

3.5.9 總結和建議115

參考文獻115

第4章 扇出型晶圓級/板級封裝124

4.1 引言124

4.2 扇出型(先上晶且面朝下)晶圓級封裝(FOWLP)125

4.2.1 測試晶片125

4.2.2 測試封裝體126

4.2.3 傳統的先上晶(面朝下)晶圓級工藝127

4.2.4 異質集成封裝的新工藝128

4.2.5 幹膜EMC層壓128

4.2.6 臨時鍵合另一塊玻璃支撐片128

4.2.7 再佈線層130

4.2.8 焊球植球131

4.2.9 最終解鍵合131

4.2.10 PCB組裝134

4.2.11 異質集成的可靠性(跌落試驗)135

4.2.12 總結和建議137

4.3 扇出型(先上晶且面朝下)板級封裝(FOPLP)137

4.3.1 測試封裝體的異質集成138

4.3.2 一種新的Uni-SIP工藝140

4.3.3 ECM面板的幹膜層壓140

4.3.4 Uni-SIP結構的層壓141

4.3.5 新ABF的層壓、鐳射鑽孔、去膠渣141

4.3.6 鐳射直寫圖形和PCB鍍銅144

4.3.7 總結和建議145

4.4 扇出型(先上晶且面朝上)晶圓級封裝146

4.4.1 測試晶片146

4.4.2 工藝流程146

4.5 扇出型(先上晶且面朝上)板級封裝148

4.5.1 封裝結構148

4.5.2 工藝流程148

4.6 扇出型(後上晶或先RDL)晶圓級封裝150

4.6.1 IME的先RDL FOWLP151

4.6.2 測試結構151

4.6.3 先RDL關鍵工藝步驟152

4.6.4 先RDL FOWLP的PCB組裝154

4.7 扇出型(後上晶或先RDL)板級封裝154

4.7.1 測試晶片154

4.7.2 測試封裝體154

4.7.3 異質集成用先RDL板級封裝157

4.7.4 RDL基板的製作157

4.7.5 晶圓凸點成型160

4.7.6 晶片-基板鍵合160

4.7.7 底部填充和EMC模塑162

4.7.8 面板/條帶轉移163

4.7.9 阻焊層開窗和表面處理163

4.7.10 植球、解鍵合和條帶切割163

4.7.11 先RDL板級封裝的PCB組裝165

4.7.12 跌落試驗結果和失效分析165

4.7.13 熱迴圈試驗結果和失效分析169

4.7.14 熱迴圈模擬174

4.7.15 總結和建議175

4.8 Mini-LED RGB顯示器的扇出型板級封裝176

4.8.1 測試mini-LED177

4.8.2 測試mini-LED RGB顯示器的SMD封裝178

4.8.3 RDL和mini-LED RGB SMD製造179

4.8.4 PCB組裝182

4.8.5 跌落試驗185

4.8.6 熱迴圈模擬185

4.8.7 總結和建議191

參考文獻191

第5章 2D、2.1D和2.3D IC集成200

5.1 引言200

5.2 2D IC集成——引線鍵合200

5.3 2D IC集成——倒裝晶片201

5.4 2D IC集成——引線鍵合和倒裝晶片201

5.5 RDL202

5.5.1 有機RDL202

5.5.2 無機RDL202

5.5.3 混合RDL202

5.6 2D IC集成——扇出型(先上晶)203

5.6.1 HTC的Desire 606W203

5.6.2 4顆晶片異質集成203

5.7 2D IC集成——扇出型(後上晶)205

5.7.1 IME的後上晶扇出型封裝205

5.7.2 Amkor的SWIFT206

5.7.3 Amkor的SLIM207

5.7.4 矽品科技的混合RDL扇出208

5.7.5 欣興電子的扇出型後上晶工藝209

5.8 2.1D IC集成210

5.8.1 Shinko的i-THOP210

5.8.2 日立的2.1D有機轉接板212

5.8.3 日月光的2.1D有機轉接板212

5.8.4 矽品科技的2.1D有機轉接板213

5.8.5 長電科技的uFOS215

5.8.6 英特爾的EMIB216

5.8.7 應用材料的互連橋217

5.8.8 台積電的LSI217

5.9 2.3D IC集成217

5.10 採用SAP/PCB法的2.3D IC集成218

5.10.1 Shinko的無芯板有機轉接板218

5.10.2 思科的有機轉接板219

5.11 採用扇出型(先上晶)技術的2.3D IC集成220

5.11.1 星科金朋的2.3D eWLB220

5.11.2 聯發科的扇出型(先上晶)技術222

5.11.3 日月光的FOCoS(先上晶)223

5.11.4 台積電的InFO_oS和InFO_MS224

5.12 採用扇出型(後上晶)技術的2.3D IC集成225

5.12.1 矽品科技的NTI225

5.12.2 三星的無矽RDL轉接板225

5.12.3 日月光的FOCoS(後上晶)228

5.12.4 台積電的多層RDL轉接板229

5.12.5 Shinko的2.3D有機轉接板229

5.12.6 欣興電子的2.3D RDL轉接板232

5.13 總結和建議247

參考文獻247

第6章 2.5D IC集成251

6.1 引言251

6.2 Leti的SoW技術(2.5D IC集成技術的起源)251

6.3 IME的2.5D IC集成技術252

6.3.1 2.5D IC集成的三維非線性局部及全域分析252

6.3.2 用於電氣和流體互連的2.5D IC集成技術254

6.3.3 雙面堆疊無源TSV轉接板256

6.3.4 作為應力(可靠性)緩衝的TSV轉接板257

6.4 中國香港科技大學雙面集成晶片的TSV轉接板技術258

6.5 中國臺灣“工業技術研究院”的2.5D IC集成259

6.5.1 雙面集成晶片TSV轉接板的熱管理259

6.5.2 應用於LED含嵌入式流體微通道的TSV轉接板260

6.5.3 集成有片上系統和存儲立方的TSV轉接板262

6.5.4 半嵌入式TSV轉接板263

6.5.5 雙面粘接晶片的TSV轉接板264

6.5.6 雙面集成晶片的TSV轉接板266

6.5.7 TSH轉接板268

6.6 台積電的CoWoS技術270

6.7 賽靈思/台積電的2.5D IC集成270

6.8 Altera/台積電的2.5D IC集成273

6.9 AMD/聯電的2.5D IC集成273

6.10 英偉達/台積電的2.5D IC集成274

6.11 台積電CoWoS路線圖275

6.12 2.5D IC集成的近期進展276

6.12.1 台積電的集成有深槽電容CoWoS276

6.12.2 IME 2.5D IC集成的非破壞性失效定位方法277

6.12.3 Fraunhofer的光電轉接板277

6.12.4 Dai Nippon/AGC的玻璃轉接板278

6.12.5 富士通的多層玻璃轉接板280

6.13 總結和建議280

參考文獻281

第7章 3D IC集成和3D IC封裝287

7.1 引言287

7.2 3D IC封裝287

7.2.1 3D IC封裝——引線鍵合式存儲晶片堆疊287

7.2.2 3D IC封裝——面對面鍵合後引線鍵合到基板291

7.2.3 3D IC封裝——背對背鍵合後引線鍵合到基板292

7.2.4 3D IC封裝——面對面鍵合後通過凸點/焊球到基板上293

7.2.5 3D IC封裝——面對背296

7.2.6 3D IC封裝——SiP中的埋入式晶片(面對面)296

7.2.7 3D IC封裝——採用倒裝晶片技術的PoP298

7.2.8 3D IC封裝——採用扇出技術的PoP300

7.2.9 總結和建議303

7.3 3D IC集成303

7.3.1 3D IC集成——HBM標準303

7.3.2 3D IC集成——HBM組裝305

7.3.3 3D IC集成——採用TSV的晶片堆疊307

7.3.4 3D IC集成——採用TSV的無凸點混合鍵合晶片堆疊311

7.3.5 3D IC集成——無TSV的無凸點混合鍵合晶片堆疊313

7.3.6 總結和建議313

參考文獻314

第8章 混合鍵合319

8.1 引言319

8.2 Cu-Cu TCB319

8.2.1 Cu-Cu TCB的一些基本原理319

8.2.2 IBM/RPI的Cu-Cu TCB321

8.3 室溫Cu-Cu TCB321

8.3.1 室溫Cu-Cu TCB的一些基本原理321

8.3.2 NIMS/AIST/東芝/東京大學的室溫Cu-Cu TCB322

8.4 SiO2-SiO2 TCB322

8.4.1 SiO2-SiO2 TCB的一些基本原理322

8.4.2 麻省理工學院的SiO2-SiO2 TCB324

8.4.3 Leti/ 飛思卡爾/意法半導體的SiO2-SiO2 TCB325

8.5 低溫DBI326

8.5.1 低溫DBI的一些基本原理326

8.5.2 有TSV的索尼CMOS圖像感測器328

8.5.3 無TSV(混合鍵合)的索尼CMOS圖像感測器329

8.6 低溫混合鍵合的近期發展332

8.6.1 IME混合鍵合的熱機械性能332

8.6.2 台積電的混合鍵合335

8.6.3 IMEC的混合鍵合338

8.6.4 格羅方德的混合鍵合339

8.6.5 三菱的混合鍵合340

8.6.6 Leti的混合鍵合341

8.6.7 英特爾的混合鍵合343

|